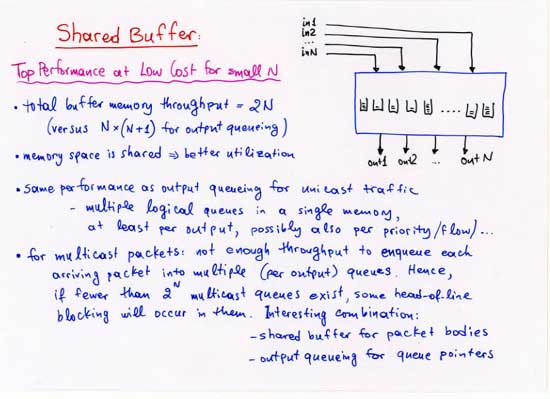

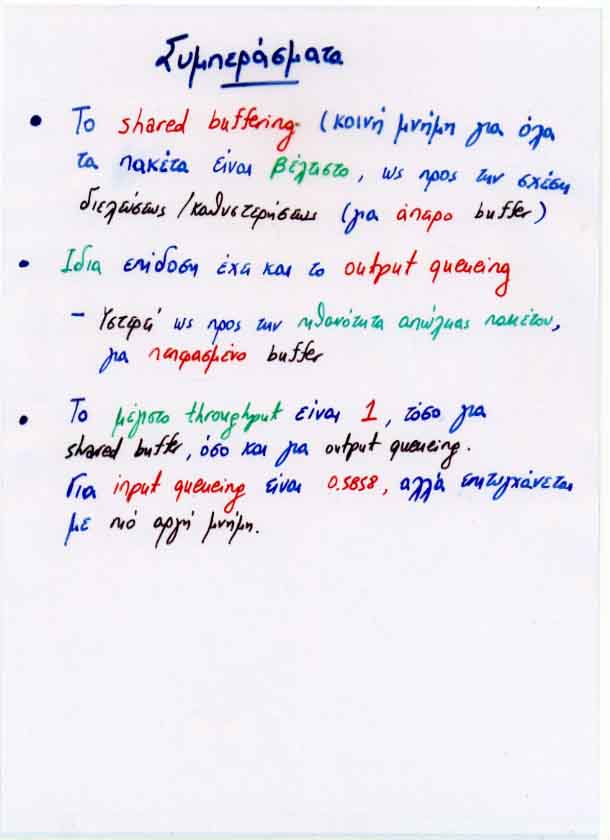

See the paper: M. Katevenis, P. Vatsolaki, A. Efthymiou: Pipelined Memory Shared Buffer for VLSI Switches, Proceedings of the ACM SIGCOMM '95 Conference, Cambridge, MA USA, 30 August - 1 Sep. 1995, pp. 39-48; USA patent number 5,774,653.

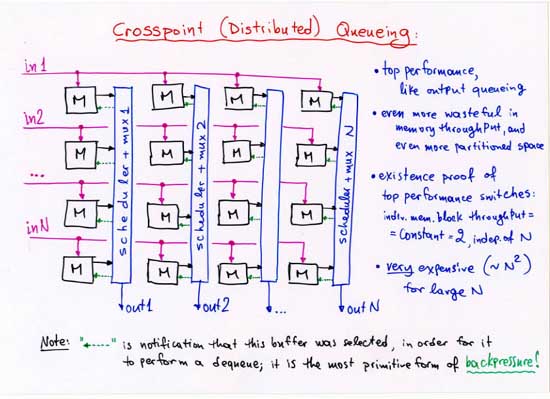

See the papers:

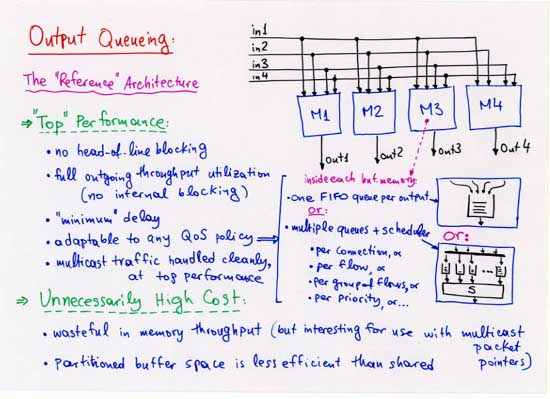

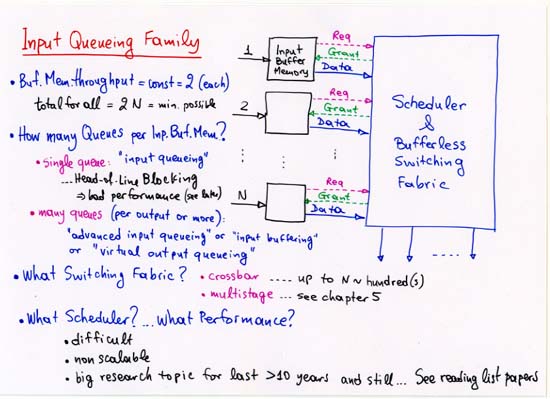

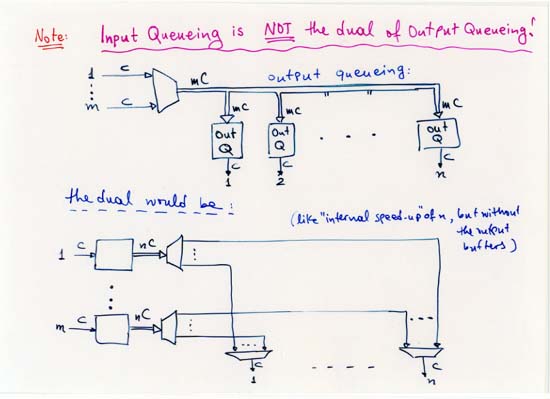

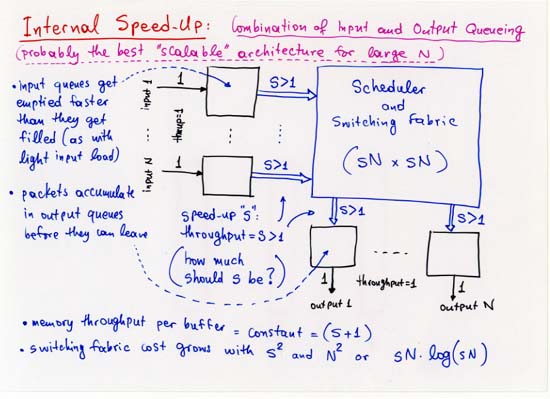

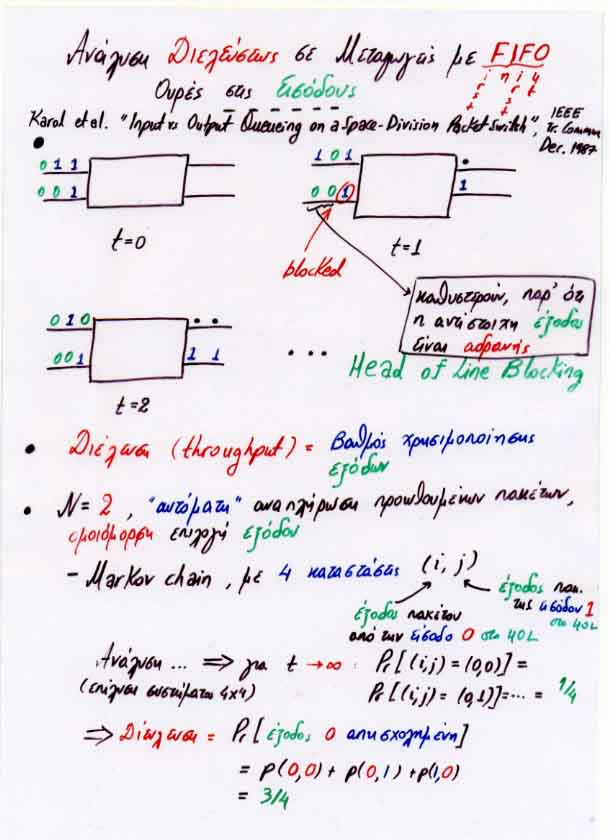

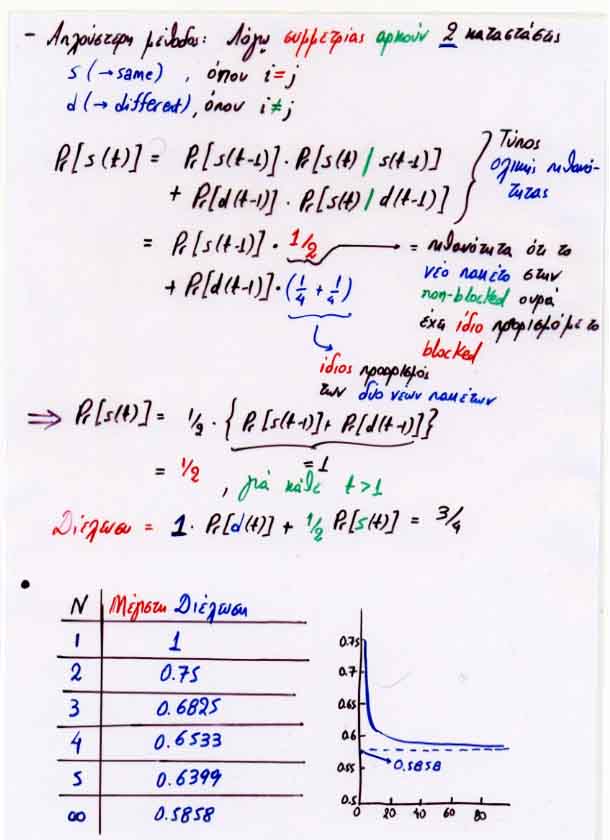

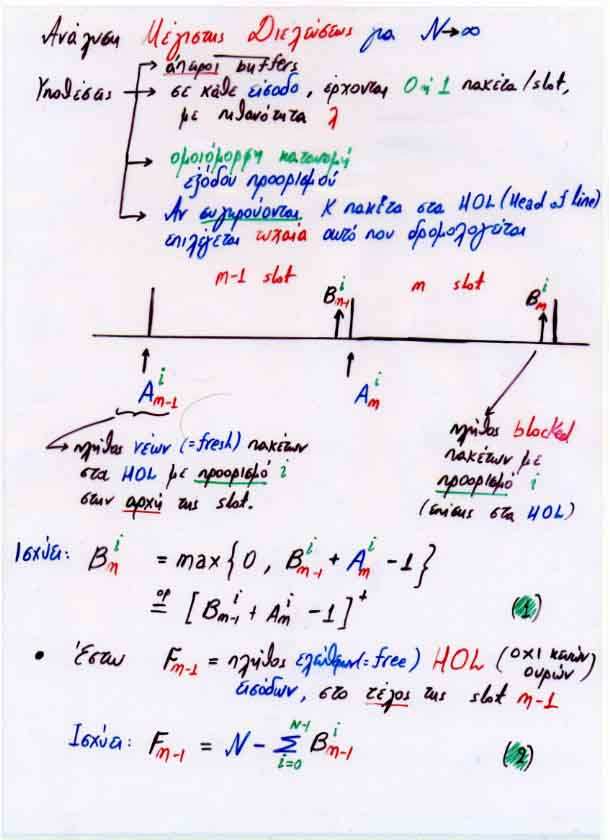

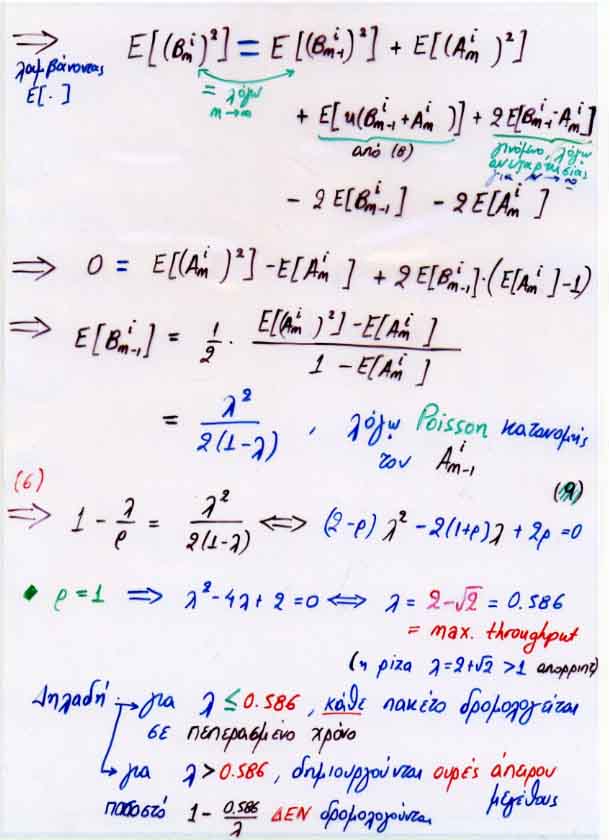

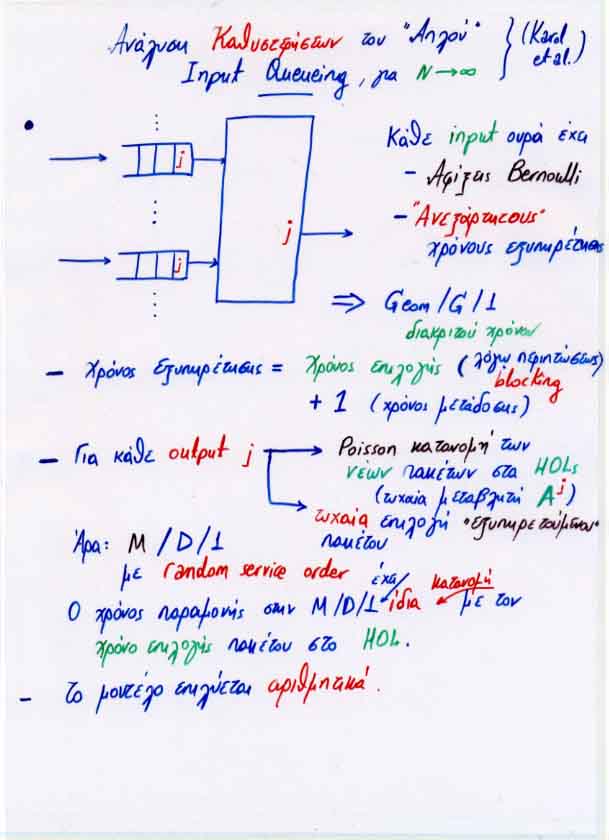

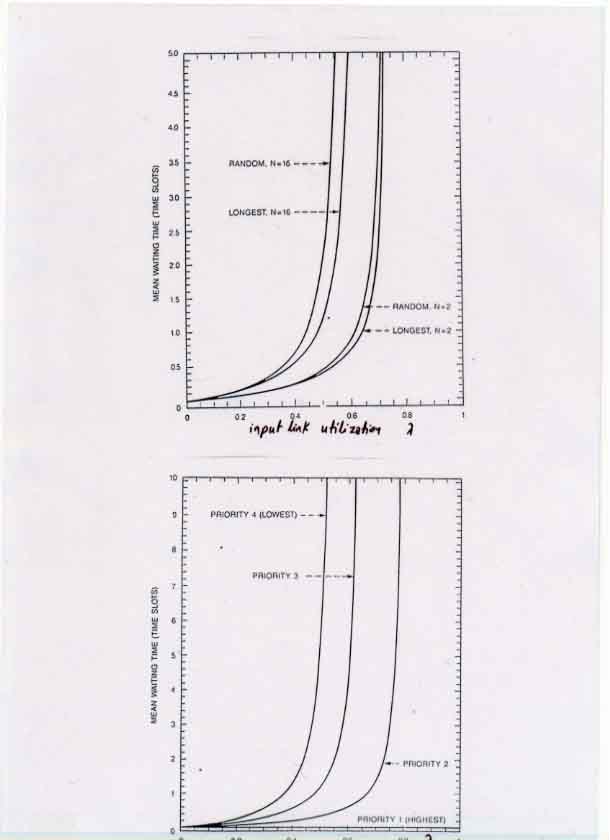

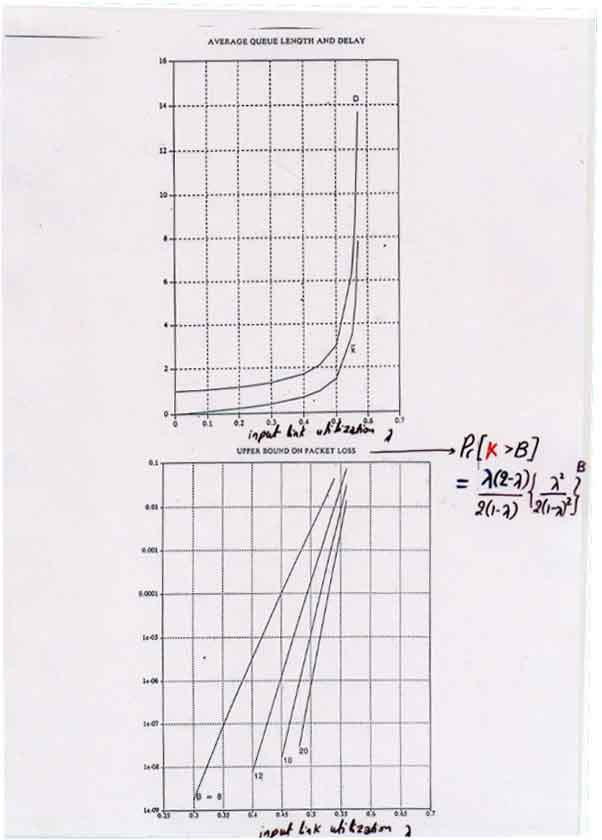

M. Karol, M. Hluchyj, S. Morgan: "Input versus Output Queueing on a Space-Division Packet Switch", IEEE Trans. on Communications, vol. 35, no. 12, Dec. 1987, pp. 1347-1356.

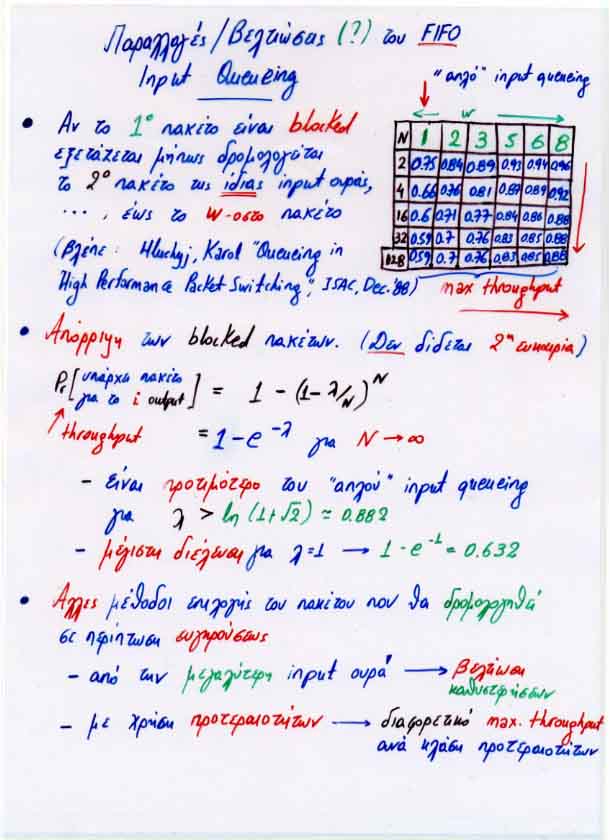

M. Hluchyj, M. Karol: "Queueing in High-Performance Packet Switching", IEEE Journal on Sel. Areas in Commun. (JSAC), vol. 6, no. 9, Dec. 1988, pp. 1587-1597.

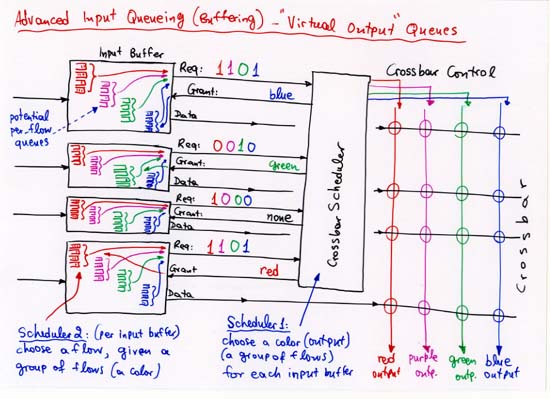

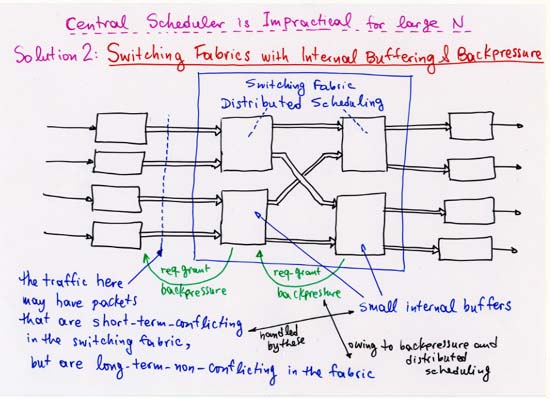

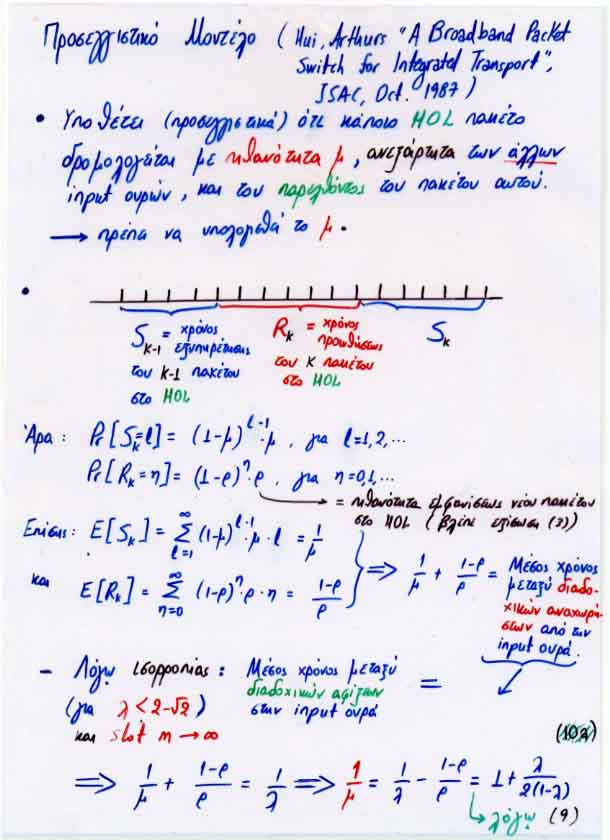

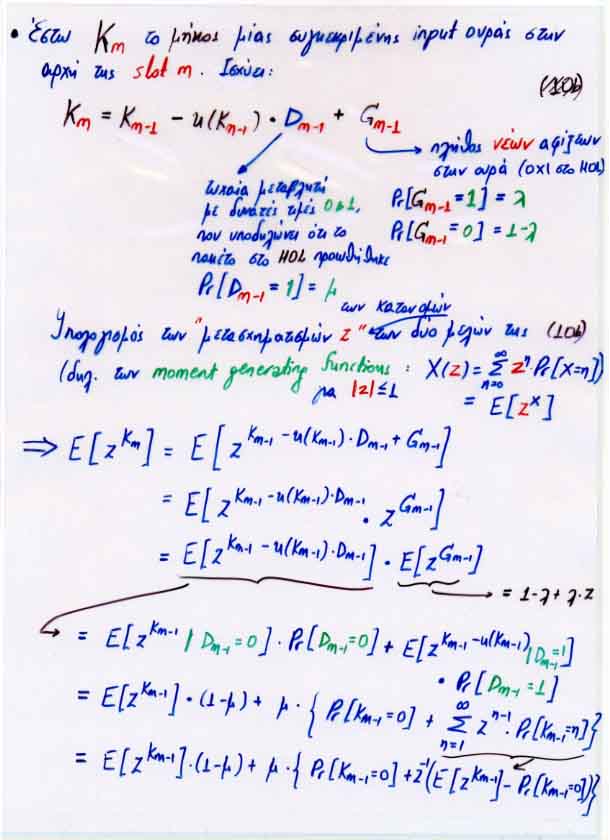

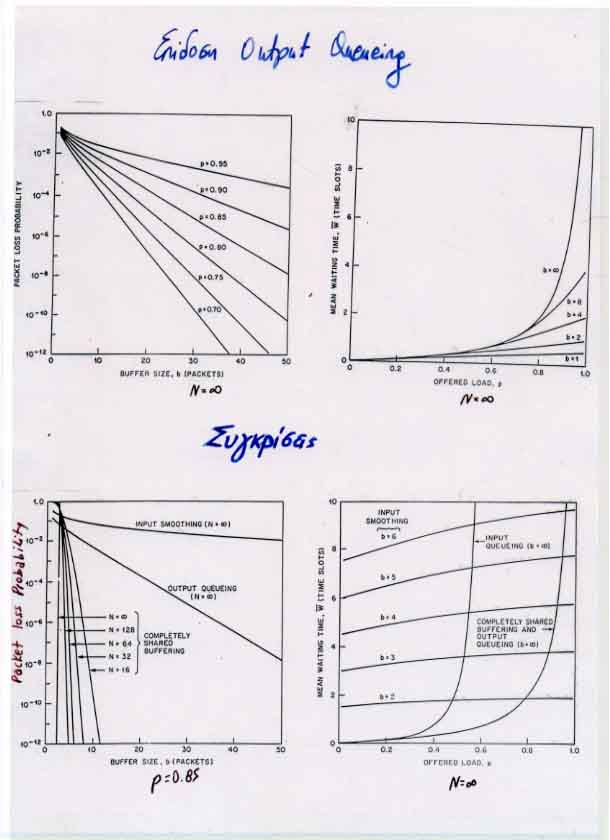

See the paper: J. Hui, E. Arthurs: "A Broadband Packet Switch for Integrated Transport", IEEE Journal on Sel. Areas in Commun. (JSAC), vol. 5, no. 8, Oct. 1987, pp. 1264-1273.

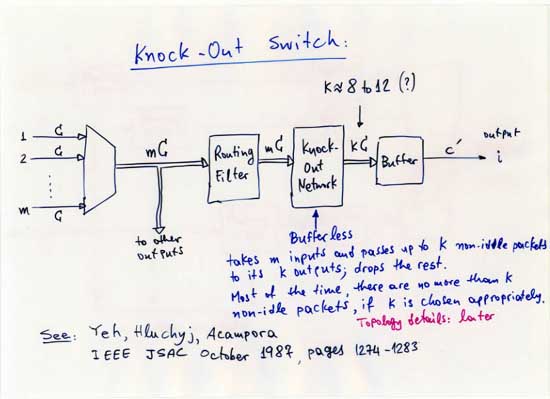

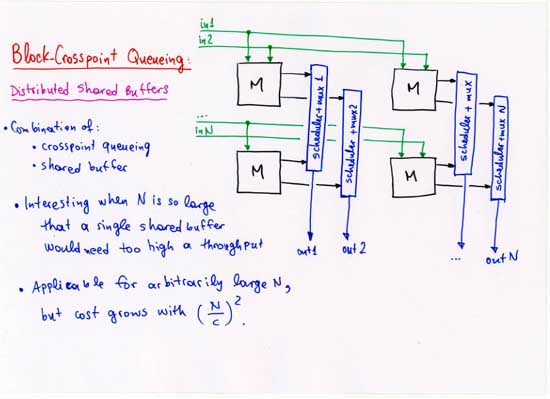

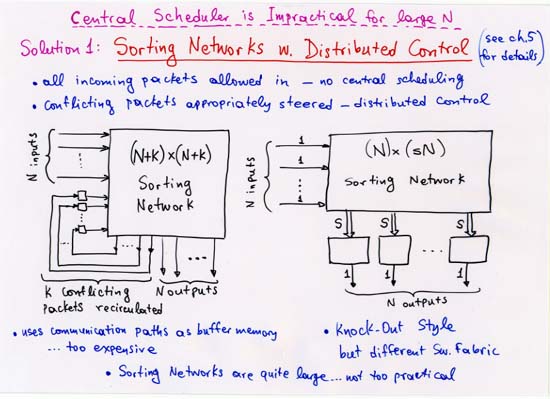

See papers number 3 through 7 in the Reading List.