| CS-534: Packet Switch Architecture

Spring 2004 |

Department of Computer Science

© copyright: University of Crete, Greece |

2.4 High-Throughput Memories for Time-Switching Shared Buffers

|

[Up - Table of Contents] [Prev - 2.3 Off-Chip Memory] |

[3.1 Queueing Arch., HOL - Next] |

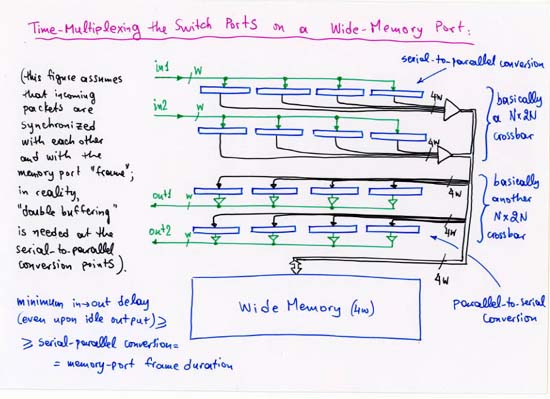

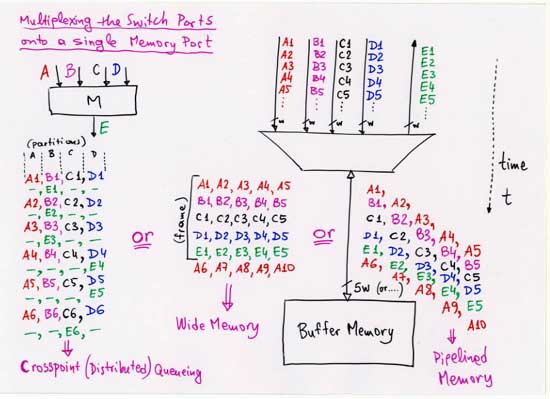

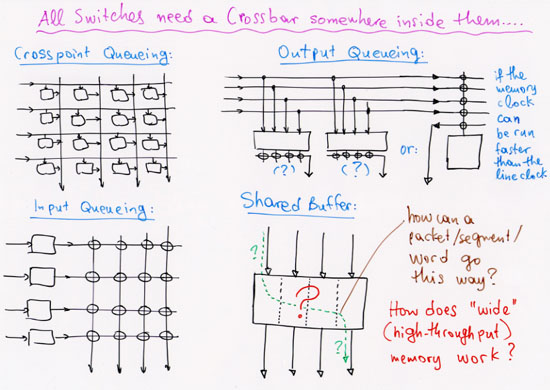

We saw in section 2.1.4 that the concept of Time Switching applied to packet switching calls for a high-throughput Shared Buffer memory into which all incoming traffic is multiplexed, and out of which all outgoing links are demultiplexed. To achieve the highest possible throughput, after exhausting the high clock frequency limits, we turn to very wide memories --as wide as packet (or cell, or segment) size allows (see exercise set 3). When multiplexing and demultiplexing the I/O links to/from the very wide memory bus, the wide-datapath techniques of section 1.3.1 have to be used. The result is reviewed in section 2.4.1; then, section 2.4.2 presents an optimized version of this wide memory, called Pipelined Memory.

2.4.1 Wide-Memory Implementation:

2.4.2 Pipelined-Memory Implementation:

Reference:

M. Katevenis, P. Vatsolaki, A. Efthymiou:

"Pipelined Memory Shared Buffer for VLSI Switches",

Proceedings of the ACM SIGCOMM '95 Conference,

Cambridge, MA USA, 30 August - 1 Sep. 1995, pp. 39-48;

http://archvlsi.ics.forth.gr/sw_arch/pipeMem.html .

FORTH, Crete, Greece (1994):

USA patent number 5,774,653 of 30 June 1998.

2.4.3 Discussion

|

[Up - Table of Contents] [Prev - 2.3 Off-Chip Memory] |

[3.1 Queueing Arch., HOL - Next] |

| Up to the Home Page of CS-534

|

© copyright

University of Crete, Greece.

Last updated: 18 Mar. 2004, by M. Katevenis. |