| CS-534: Packet Switch Architecture

Fall 2001 |

Department of Computer Science

© copyright: University of Crete, Greece |

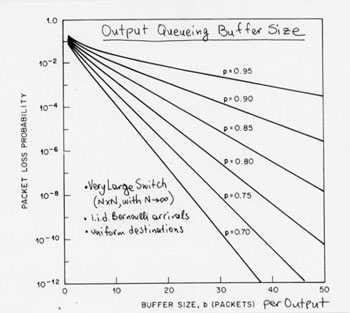

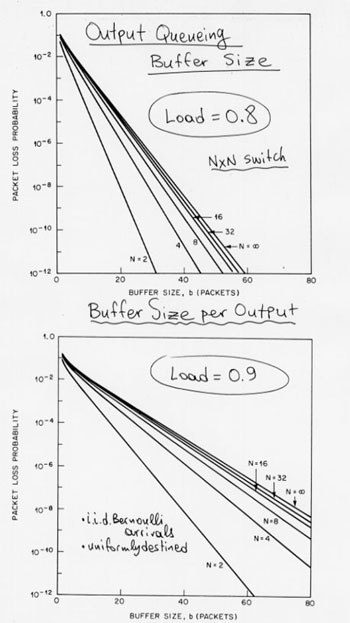

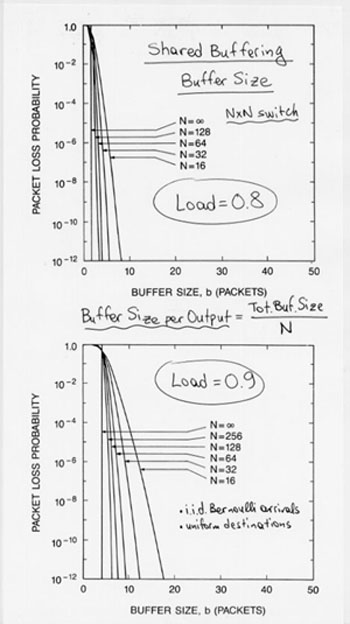

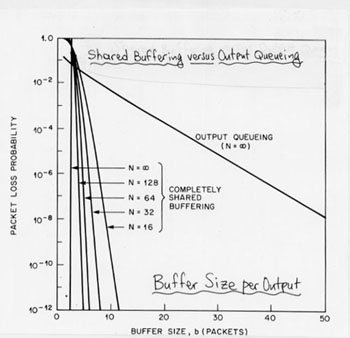

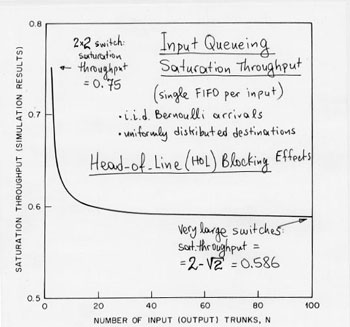

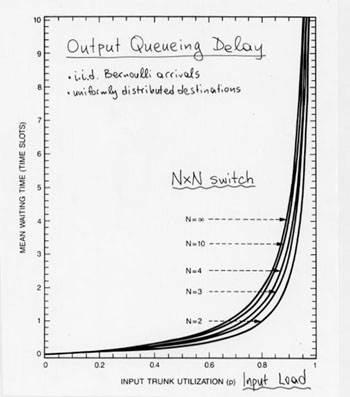

Buffer Space Requirements:

When the incoming traffic consists of fixed-size packets

from independent, identically distributed (i.i.d.) Bernoulli processes,

with uniformly-distributed destination (output) ports,

analysis and simulation have yielded the results plotted below

--primarily from the Hluchyj and Karol JSAC paper of December 1988

referenced below (© copyright IEEE).

Attention:

results derived for i.i.d. Bernoulli (non-bursty) arrivals,

with uniformly-distributed destinations (no overloaded hot-spots),

are only useful for gaining a rough, first insight

into the behavior of systems,

but are often not representative of the real behavior of systems

under real traffic!...

© copyright IEEE --primarily from the Hluchyj and Karol JSAC paper of December 1988 referenced below.

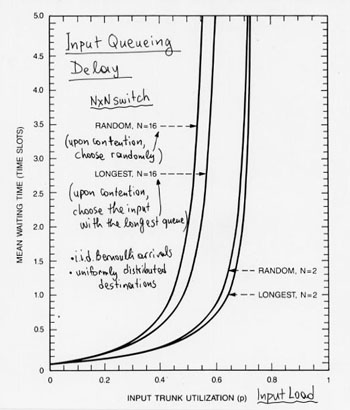

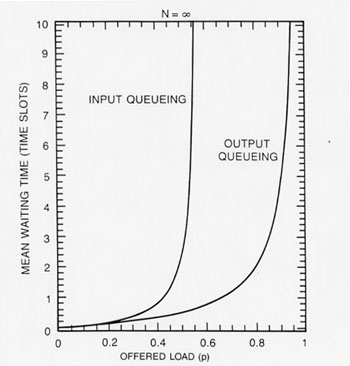

Throughput and Delay

under Input Queueing with Head-of-Line (HOL) Blocking:

When the incoming traffic consists of fixed-size packets

from independent, identically distributed (i.i.d.) Bernoulli processes,

with uniformly-distributed destination (output) ports,

analysis and simulation have yielded the results plotted below

--primarily from the Hluchyj and Karol JSAC paper of December 1988

referenced below (© copyright IEEE).

Attention:

results derived for i.i.d. Bernoulli (non-bursty) arrivals,

with uniformly-distributed destinations (no overloaded hot-spots),

are only useful for gaining a rough, first insight

into the behavior of systems,

but are often not representative of the real behavior of systems

under real traffic!...

References:

Reference:

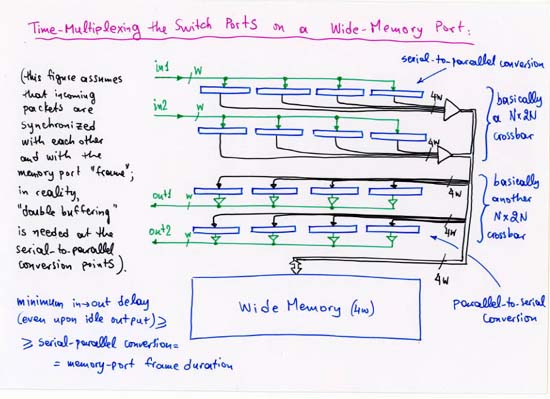

M. Katevenis, P. Vatsolaki, A. Efthymiou:

"Pipelined Memory Shared Buffer for VLSI Switches",

Proceedings of the ACM SIGCOMM '95 Conference,

Cambridge, MA USA, 30 August - 1 Sep. 1995, pp. 39-48;

http://archvlsi.ics.forth.gr/sw_arch/pipeMem.html .

FORTH, Crete, Greece (1994):

USA patent number 5,774,653 of 30 June 1998.

Bibliographic references: click here

Bibliographic references: click here

| Up to the Home Page of CS-534 |

© 2001 copyright: University of Crete, Greece.

Last updated: 29 Nov. 2001, by M. Katevenis. |