| CS-534: Packet Switch Architecture

Spring 2003 |

Department of Computer Science © University of Crete, Greece |

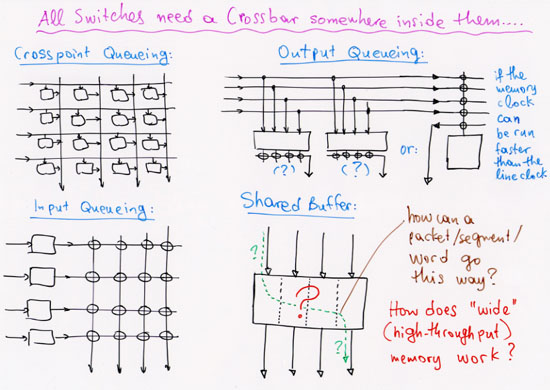

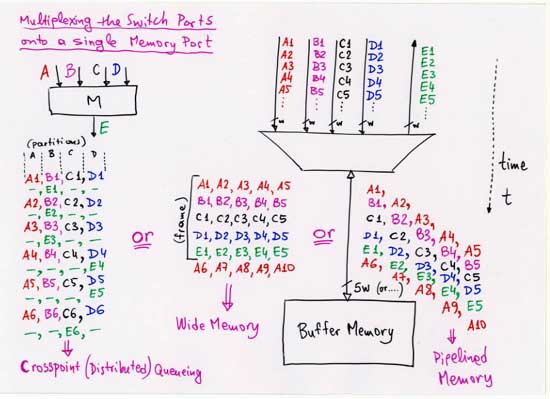

4.2 Shared Buffer and High-Throughput Memory Implementation

|

[Up: Table of Contents] [Prev: 4.1 Output Queueing] |

[Next: 4.3 Shared Buffer Impl.] |

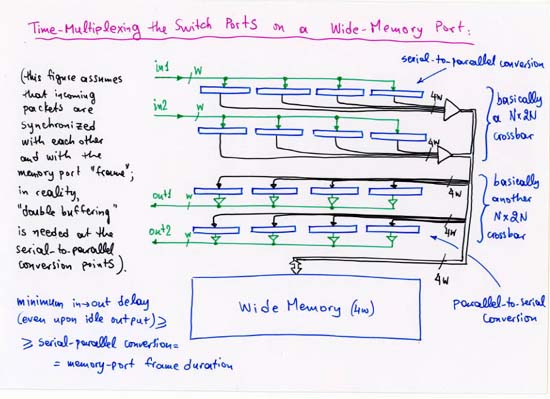

Wide-Memory Implementation:

Pipelined-Memory Implementation:

Reference:

M. Katevenis, P. Vatsolaki, A. Efthymiou:

"Pipelined Memory Shared Buffer for VLSI Switches",

Proceedings of the ACM SIGCOMM '95 Conference,

Cambridge, MA USA, 30 August - 1 Sep. 1995, pp. 39-48;

http://archvlsi.ics.forth.gr/sw_arch/pipeMem.html .

FORTH, Crete, Greece (1994):

USA patent number 5,774,653 of 30 June 1998.

|

[Up: Table of Contents] [Prev: 4.1 Output Queueing] |

[Next: 4.3 Shared Buffer Impl.] |

| Up to the Home Page of CS-534

|

© copyright

University of Crete, Greece. Last updated: 9 May 2003, by M. Katevenis. |