![[photograph of Manolis Katevenis]](photos/2019_10_05.MGHKatevenis.jpg)

Manolis G.H. Katevenis

Professor Emeritus,

Department of Computer Science,

University of Crete;

Founder & Honorary Head,

Computer Architecture and VLSI Systems (CARV) Laboratory,

Institute of Computer Science (ICS),

Foundation for Research & Technology - Hellas (FORTH),

Heraklion,

Crete,

Greece.

Home Page:

https://users.ics.forth.gr/~kateveni/

E-mail:

kateveni papaki ics teleia forth teleia gr

Tel:

+30 - 2811.39.16.64 (ICS office),

+30 - 2810.39.35.64 (CSD office)

Address (Postal and Courier):

FORTH-ICS, 100 Plastira Ave, Vassilika Vouton, Heraklion, Crete,

GR-70013 GREECE.

UoC-CSD Visiting Address and Office Hours:

Room K329, Computer Science Building;

usually Mondays and Fridays 11:00 - 11:30

(please call or email before coming, for confirmation and appointment).

FORTH-ICS Visiting Address: Room AA282, East Campus,

ICS, FORTH

(more local and travel info, from HiPEAC'11).

Areas of Interest:

– Computer Architecture:

Scalable Manycore / Multiprocessor / Warehouse-Scale

System Architecture for High Performance Computing (HPC) and Big Data;

Exascale Computing; RISC-V;

– Interprocessor Communication:

Memory-to-memory communication and synchronization

– remote-DMA, remote-enqueue;

Lean, low-latency Network Interfaces;

– Interconnection Network Architecture;

– VLSI Systems.

Founding member of the European Network of Excellence (NoE) on

High-Perfomance and Embedded Architecture and Compilation (HiPEAC)

Member of

Academia Europaea

– The Academy of Europe (see also

www.AE-Info.org

for more information of general interest)

Stelios Pichoridis Award

for Outstanding University Teaching

– jointly with Charalampos Katerinopoulos –

University of Crete, 2015:

Lecture Slides

[PDF]

[and a TV conference at TV Creta]

Award by the Secretary General of the Region of Crete, 2003

– jointly with Stelios Orphanoudakis

and Panos Constantopoulos –

as the Principal Organizers of the Department of Computer Science,

University of Crete.

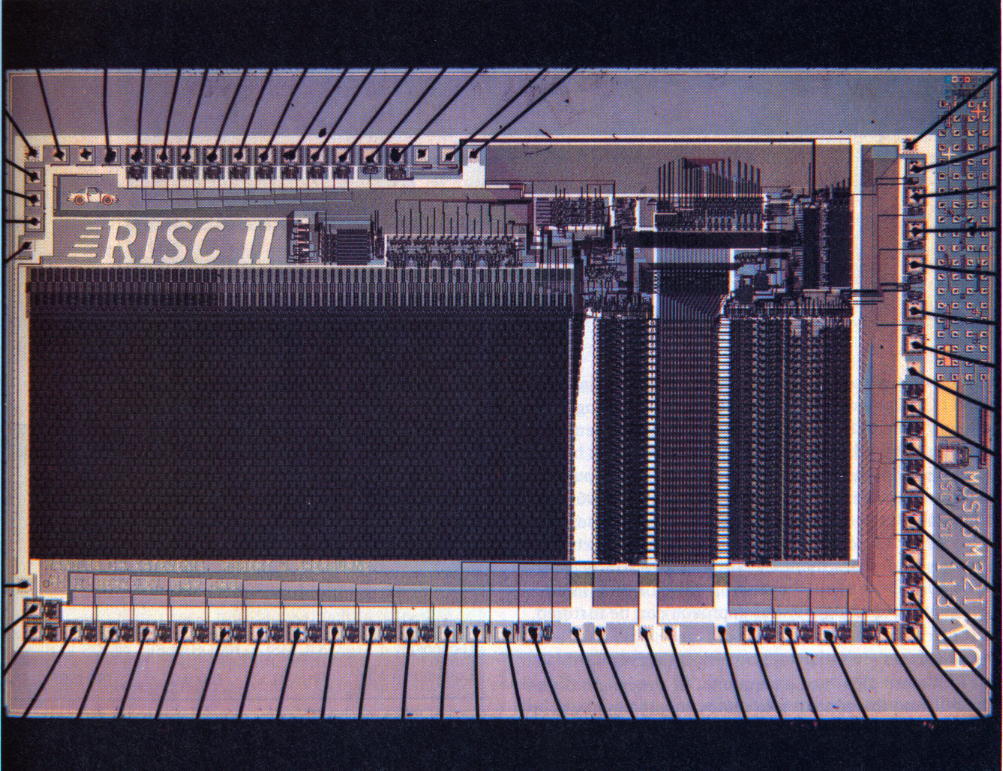

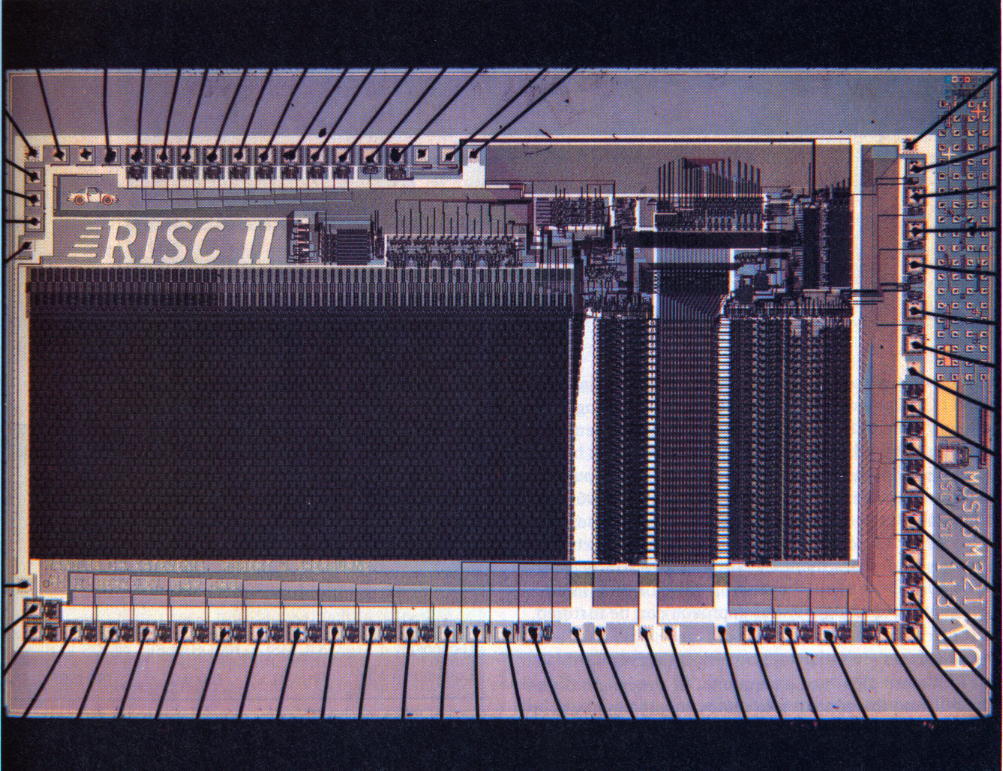

ACM Doctoral Dissertation Award 1984

"For his dissertation

Reduced Instruction Set Computer (RISC) Architectures for VLSI."

Member of

Academia Europaea

– The Academy of Europe (see also

www.AE-Info.org

for more information of general interest)

Stelios Pichoridis Award

for Outstanding University Teaching

– jointly with Charalampos Katerinopoulos –

University of Crete, 2015:

Lecture Slides

[PDF]

[and a TV conference at TV Creta]

Award by the Secretary General of the Region of Crete, 2003

– jointly with Stelios Orphanoudakis

and Panos Constantopoulos –

as the Principal Organizers of the Department of Computer Science,

University of Crete.

ACM Doctoral Dissertation Award 1984

"For his dissertation

Reduced Instruction Set Computer (RISC) Architectures for VLSI."

–

Full text of the Dissertation

available on-line

–

In 2015, the RISC Project was recognized as an IEEE Milestone.

–

The RISC-V

free and open standard Instruction Set Architecture

is an evolution of that project.

Detailed Curriculum Vitae (HTML version of July 2021)

[or PDF version];

includes

Biography

and full lists of:

publications,

grants,

conference organization,

invited lectures,

students, and

courses

Brief Biography (2013)

(or Greek version (2013))

(or very short version (2012)).

Older (March 2011) list of

Publications by topic,

with pointers to the corresponding project pages.

Research Projects:

-

Interconnection Network Architectures: currently in the

NET4EXA

and previously in the

RED-SEA

EuroHPC projects

-

Other current Computer Architecture & VLSI projects

in the CARV Laboratory:

-

Recent projects in Exascale System Architecture:

-

Previous projects, 1992-2013:

Teaching:

-

CS-120: Digital Design

(Fall semesters since 2002).

[Private local]

-

CS-225: Computer Organization

(Spring semesters since 2014,

as well as many spring semesters since the late 80's).

[Private local]

-

CS-534: Packet Switch Architecture

(graduate course - Sp'15 with N. Chrysos;

Sp'13, and most spring semesters before that since the mid-90's)

[obsolete 2nd copy].

-

CS-121: Electric Circuits

(Sp'12, Sp'11, Sp'10)

[2nd copy].

-

CS-425: Computer Architecture

(F'06; F'04; F'03; F'00; F'99, F'96, and older).

-

CS-422: Introduction to VLSI Systems

(F'02, F'00, F'99, Sp'98, and older).

Others:

© Copyright 1998-2023 Manolis Katevenis.

Last updated: Summer 2024.

![[photograph of Manolis Katevenis]](photos/2019_10_05.MGHKatevenis.jpg)